UNIT-V. - Processing and Operating Systems

## Introduction:

⇒ Microprocessor execute Simple user applica -tion program. But some application requises large number of line of code. Writing and executing large program on microprocessor is complex task.

⇒ To study the writing complex program for microproce\$\$091. We must understand concept of proce\$\$ and OS.

⇒ The process difines the state of an executing program, which the OS provides the mechanism for switching execution between the processes.

⇒ These two mechanisms together let us build

⇒ These two mechanisms together let us build applications with more complex functionality and much greater flexibility to saying satisfy timing requirements.

Multiple Tasks and Multiple Processes: > Task are units of sequential code implementing the system actions and executed concurrently by an OS. ⇒ Real time systems requires that tasks be performed within a particular time function. Task is related to the performance of the great time systems.

⇒ A task, also called a thread, is a simple program that thinks it has the CPU all to itself. The design process for a real-time application envolves splitting the work to be done tasks responsible for a real-time application i.e. a portion of the problem.

> Each task is assigned a priority, its own set of CPU registers and its own stack area.

⇒ In the specified time constraint, system must produce its correct output. If system fail to meet the specified output, then the system is fail or quality decreases.

⇒ Real time systems one used for space flights, air traffic control, high speed aircraft. telephone switching electricity distribution, industrail process etc.

⇒ Real time system must be 100% responsive 100% of the time. Response time is measured in fab foractions of second, but this is an ideal not often advieved in the field.

> Real time database is updated continuously. In aircraft example, flight data is continuouely changing so it is necessary to update. It include speed, direction, location, height etc. ⇒ A process is a sequential program in exection Terms like jub and task are also used to denote a process. > A process is a dynamic entity that executes a program on a particular set of data. Multiple privcesses may be associated with one program. ⇒ Task is a single instance of an executable porogeram. > In a multiprogramming environment, usually more programs to be executed than could possibly be sun at one time. In CPU scheduling it switches from one process to another process. cpu sussource management is commonly known as scheduling. > Objective of the multiprogramming is to increases the CPU utilization. CPU scheduling is one kind of fundemental operating system functions. => Each process has an execution state which indicate What process is cuspently doing. The process descriptor is the pasic data structure used to represent the Specific state for each process.

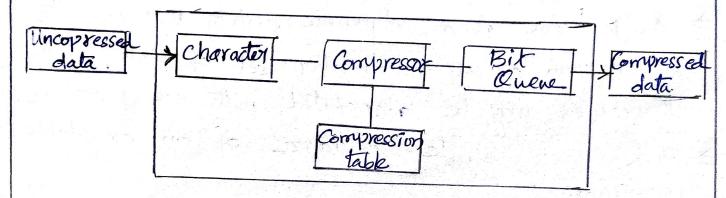

⇒ Input and output of the compressoon box is social ports. It takes uncompressed data and processes it. Output of the box is compressed data. Given data is compressed using predefined compression table. Modern is used such type of box.

> The program's need to receive and send data at different rates. It is an example of rate control problems. It uses asynchronous input. You can provide a button for compressed mode and uncompressed mode.

⇒ when used press uncompressed mode, the input data is passed thronough unchanged. ⇒ Sampling the button's state too stoudy can cause the machine to miss a button depression entirely but samplying it too frequently and duplicating a data value can cause the machine to incorrectly compress data. ⇒ This problem is solved by maintaining counter.

Multirate Systems:

> More complicated control systems have multiple sensors and actuators and must support control loops of different rates. Multinate embedded computing systems includes automobile engines, printers and cell phones.

> Tasks may be synchronous or asynchronous. Synchronous tasks may recur at different plates. Processors run at different rates based on computational needs of the tasks.

> Automotive engine control is an example of multistate system. Tasks in automotive engine control one spork control, crankshift sensing fuel/air mixture, oxygen sensors and kalman filter.

> The figure shows automotive engine control. > The sport plug must be fired at a certain point in the combustion cycle, but to obtain better performance, the phase relationship between the piston's movement and the spark should change as a function of engine

> Using a microcontroller that senses the engine crankshaft position allows the sport timing to vary with engine speed. Engine \* Automobile engine Controllers use Control additional sensors, including the gas Engine pedal position and Control an oxygen sensor used to control emissions. They also use a multimode control scheme. > The looger number of sensors and modes increase the number of discrete tasks that must be performed.

Process State and Scheduling:

⇒ Each process has an execution state which indicates what process is convently doing. The process descriptor is the basic data structure used to represent the specific state for each process.

> A state dragtan is composed of a set of state and transition between states.

Build contexts ( Ready Admint, State Create request New! Start Lin Conne Running Therminali End) Slate , the Exiting (Waiting state) Controlled by Controlled by CPU Scheduler Job Scheduler 87-1-

=> State diagram is used by process manager to determine the type of service to provide to "The process. The process states are as follows: "New, ready, running, waiting and end. NEW: operating system creates new process by using forthe system call. These process are newly created privers and resources are not allocated. Ready: The process is competing for the CPU. Process sreaches to the head of the list (queue) Running: The process that a currently being executed. Operating system allocates all the hardware and software presources to the process for execution. waiting: A process is waiting until some event occurs such as the completion of an input-output operation. Exit/End: A process is completes its operations and releases it all resources.

> Five types of inter-process communication as follows: 1. shared memory permits processes to communicate by simply reading and writing to a specified memory location. 2. Mapped memory to is similar to shared memor except that it is associated with a file in the file system. 3. Pipes point sequential communication from one process to a related process. 4. FIFOs are similar to pipe, except that unrielated prioresses can communicate because the pipe is given a name in the file system 5 Sockets supports communication between unordated privesses even on different Computers. Purposes of IPC: I. Data Transfert: one process may wish to send data to another process. 2. Sharing Data: Multiple processes may wish to operate on shared data, such that if a process modifies the data that change will be immediately visible to othing processes sharing it=

INTERPROCESS COMMUNICATION MACHANISM:

> Exchange of data between two or more Separate, independent processes / threads is possible using IPC, Operating systems provides facilities /resources for Inter-Process Communication (IPC), such as message queues, semaphores, and shared memory. A complex programming environment often Uses multiple cooperating perograss processes to perform gielaxed operations. These processes must communicate with each other and share resources and information. The Keynel must provide mechanisms that make this possible. These mechanisms are collectively neferred to as enterprices Communication. > Distruibuted computing systems make use of

⇒ Distruibuted computing systems make use of these facilities/resources to porovide Application Priogramming Interface (API) which allows IPC to be priogrammed at a higher level of abstraction (e.g. send & receive)

Five types of inter-priverse communication are as follows: 1. Shared memory poimite processes to communi--cate by simply reading and writing to a specified memory location. 2. Mapped memory is similar to shared memory, except that it is associated with a file in the file system. 3. Pipes point sequential communication from one process to a related process. 4 FilFOs are similar to pipes, except that unorelated processes can communicate because the pipe is given a name in the file system. 5. Sockets support communication between unordated porocesses even on different computers. Pumposes of IPC: One process may wish to Send data to another 1. Data transfer: p910088-

2. Sharing date: Multiple processes may wish to operate on shared data, such that to change will be immediately visible to other processes showing it. 8. Event modification: A process may wish to notify another process or set of processes that some event has occurred. 4. Resource shaving: The Kernel provides default semantics for resource allocation: they are not suitable for all application. 5. PHORESS control: A process such as a debugger may wish to assume complete control over the execution of another process. IPC has two forms: IPC on same host IPC on different hosts. IPC is used for 2 functions: 1. Synchronization 2. Message passing.

Features of Message Passing: 1. Simplicity; It should be possible to communicate with old and new applications. 2. Uniform semantics: Message passing is used for two types of IPC. a. local communication " Communicating processes core on the same node. b. Remote communication: communicating processes ave on the different nodes. 3- Eifférieur: IPC become so expensive if message passing system is not effective 4 Reliability: Distributed systems are prone to different catastrophic event such as node crashes ON physical link failure. Loss of message because of communication tink fails. To handle the loss message, we required acknowledgement and stetransmission policy. 5. Convectness: It is a feature to IPC provides for group communication. I ssues related to correctness to a epiloup of receivers will be delivered to eithog all of them of none of them

(i) Automicity: Every message sent to a group of necesivers will be delivered to eithor all of them or none of them (ii) Ordered delivery: Message arrive to all receivers in an order acceptable to the application. (ii) Scorvivability: Message will be conrectly delivered despite partial failures of processes, machine or communication 6) Security : Message passing system must provide a secure end to end communication. 7) Pontability: message passing system should stelf be positable IPC Message passing: > Message passing system plequires the Synchronization and communication between the two processes > The actual function of message passing provided in the form of a pair of primitives. (a) Send Coestination\_name, message, (a) Receive CSOUTCE\_name, message)

Design characteristics of message system for IPC 1) Synchronization between the process. 2). Addressing 3) Format of the messege 4) Queueing discipline. Message structure Actual structural information Sequence Addresses data or Number of number Receiving Sending pointor to bytes/ Type or message Process process the data dements ID address address K Variable X < - Fixed-length Size collection header. of typed data => The header block of a message may have the following elements: 1. Address: A set of character that uniquely édentify both the sender and receiver. 2. Sequence number: It is the message identifier to identify duplicate and last message in case of system failure. 3. Structural enformation: It has two part. 1) The type poort that specifies whether the data to be sent the receiver is included within the message 2) length of the Variable - Size message.

Sharled Memory. A region of memory that is shared by Co-opening processes to established. Processes can be then cochanged information by reading and Writing data to the shared region > shared memory allows maximum speed and convenience of communication, as it can a computer. > shared memory Cliend > Shared Memory > Server message passing => In contrast, in shouldmemory, the system calls are required only to establish, shoud mem. Kegnel regions. Advantages: Output file (Input file 1. God for shaving large amount of data 2. Very fast. limitations. > NO synchronization meat their own. provided - application must

Evaluating Operating System Performance. Scheduling algorithm is not used for calculating performance of the real system sunning policieses. Assumption about analysis of scheduling policy one as follows: 1. Context switching time is 2010, But context. Switching adds significant delay in some Cases. 2. context switching time is zero, we know in advance, the execution time of the processor. 3. Cache conflicts among processes can drastically degrade process execution time. · context switch overhead represents the worked associated with preempting current job, saving its content, loading the cotext of the next job and resuming the next job. The context switch into task (Ti) is performed at the Kernel priority level, but only when task CTi) is neady to execute. · Figure next shows the scheduling the context switch overheads in a time-torgered preemptive System.

consider two tasks TI with CI = 10 and T2 with C2>17. clock interrupt handled is envoked with poured To=8 and computation time G=1. • The execution of the Task T2 is regularly preempted by the clock handler. Somewhere before the second clock tick TI is greateased the presenter the SC'SS'SC The Clock tick I Event 1 Scheduling Context Switch overhead scheduling (S) and context switch (C) overheads in a time-tiggered preemptive system. > files executing for 10 time units TI is finished and released the processor until the next dock tick, During the next scheduley invocation the process is switched back to Tz.

Power optimization strategies for Broceses. 52 Power management policy in general examines the state of the system to determine when to texe actions. Power management policy is a strategy for determining when to portorin contain power mangement operations. => Dynamic Power management (DPM) is a design methodology for dynamically reconfiguring system to provide the suguesting services & performance levels with a minimum vuniber of active components of a viringen Noad on such components. A going into a low-power mode takes time. generally, the more that is shut off, the longer the delay incubied during sestant. Because power-down and power-up are not free, modes should be changed coughly

## Scanned with ACE Scanner

=> In most real-time operating systems, a context switch requires only a few hundred instruction, which with only slightly more overhead for a Simple real-time scheduler like RMS. When the overhead time is very small relative to the task periods, then the zero-time context Switch assumption is often a neasonable approximation.

⇒ Process execution time is not contant. Extra CPU time can be good. Extra CPU time can also be bad because next process runs earlier. causing new preemption.

⇒ Processes can cause additional caching problems. Even if individual processes one well-behaved, processes may intoffere with each othol.

⇒ Worst-execution time with bad behavior

is usually much more worse than

And and and an and a first and

execution time with good cache

그는 사람은 소행을 가장에 지난 사람들은 것이 가지 않는 것을 가지 않는다.

behavion.

A Determining when to switch into and out of a power-up more requires an analysis of the overall system activity. I System-level power management saves power & subsytems. Examples of devices include 1/0 controllers, have disk drives, network integrace cards and displays. Shutting down have disks and displays is the most widely adopted systemlevel powor maragement on PCs. Power management concept Requises Requises. Busy Idle Busy Power state working Ted Sleeping Two working State workload Consists of multiple requests. For thard disks, requests are read of write commands; for network coards, requests one packets to send of to be received." I when there are requests, the device is busy: otherwise, it is ville. Here, the device is ville between TI & TA, when the device is idle, it can be shut down to enter a low-power sleeping state. => The device is shutdown at T2 and woken up at T4 when requests arrive again. Changing power states takes time: Ted and Two are the Shandown and wate-up delays.

It takes several seconds to wake up these devices Furthermore, naking up a sleeping device may take extern enongy. rendictive shutdown: shutdown as soon as a new edle period slarts based on history. Avoid wasting energy before reaching timeout threshold. Predictive water : water when predicted idle time expires, even if no new activity has occurred. . Use a regression of of peredict the length of this holp idle pouled based on preceding active previous and posis por previous n pairs of idle / active periods. Predictive shutdown: Observe short active period tends to be followed by long idle poriod in some applications. If the preceding active pocied is less than as thoushold, the idle pourod is predicted to be longer than break-even. time. Advanced Configuration and Power Intestace Advanced Configuration and Power Interface (ACPI) is an open industry standard for power management services. It is designed to be compatible with a wide variety of as.

=> Power management states and required functionality are defined for multiple levels of the system. 1. Global View: Gx states 2. System : Sx states 3. Processon: Cristates 4. PCI/PCI-X bus: Bx states 5. PCI/express links: Lx states 6. Devices : Dx states · General triend of the state numbers: (Zero) O is the active state (example: GO, SO, DO). System is available to user. The state number 1 ton are sleep states. Higher number corresponds to lower power. User perception is OFF for all of these Sleep State. · ACPI functions ave as follows: 1. System power management 2. Device power management 3. Perocesson power management 4. Plug and play 5. system events 6. Brittery managements. 7. Thermal monagement 8. Emberded controller.

I The following figure ACPI system was designed to enable the operating system to set up and control the individual navidware components. User Interface ACPI nun-time components 1. ACPI tables: Describe the Operating System interface to the hardward. 2. ACPI registers : The constrained Part of the hardware interface Policy manager Device drivers described (at least in location by the ACPI Subsystem description tables. Subsystem ACPI 3. ACPI BLOS: related ACPI system firmwate hardware The fighnwate boots ACPI BLOS ACPI System the machine and compatible with ACPI spec-Global System states C3-P910Cesson Stopped · GO: Working (System operational) Cache ignore snoops • G1: Sleeping-no used threads system Looks off Device power states D3: off-power off to device · G2/85: Soft off D2: Less power than Di DI: Less power than Do · G3 : Mechanical off Do : Fully-on. Processon power states: · Co: Full power, instruction execute CI: P910 (esson slopped, Less power oban G 24

& Power interface & its Advanced Configuration to a complete System. relationship Applications dependent application APIS OSPM KERNEL System code OS Specific ACPI driver/ Device technologies, AML interprater drive Interfaces & Code OS indepedent ACPT ACPY table ACPI technologies register BIDS Interface Interfaces intesface Interface Code and hardware registers ACPI BIDS ACPI tables Platform Hardware Blos Sleeping States: S3: Low latency steeping state SO: system working DRAM still maintained 81: Ion latency sleeping St: lowest power longest State Processor context maintained Wake-up DRAM not maintained S2: Low latency sleeping sleeping S5: Soft off state State Processor Context not maintained. 25

Example Real Time Operating Systems.

## Posix

- ⇒ POSIX that stands for Portable Operating System interface is a standard that is being jointly developed by the IEEE and the Open Girrup. It defines a standard Operating system interface and environment, including a command interprete (or shell), and common utility program to support applications portability at the source code level. The current revision of POSIX is The Open Group Base specifications Issue 6 and also the IEEE std. 1003.1:2001

- The pasix standard describes the behavior of a computer system as seen through a particular set of data types, function interface and system utilities. The standard describes an interface not an implementation.

⇒ There is no particular distinction between system functions and library functions, as the CAA libraries are included with the POSIX libraries.

⇒ The basic goal was to promote portability of applications programs across UNIX system environment by developing a clear, consistent and unambiguous standard for the interface specification of a portable

operating system based on the UNIX system documentation. The standard codifies the common. existing definition of the UNIX system. • The standard is composed by four major components: 1. Base refinitions: Jhis includes general terms, concept and interfaces common to entre standard. 2. System Interfaces: This comprises the definitions for system service functions for the c programming language, function and postability issues, enound handling and glecovery. 3. Shell and Utilities: It contains the definitions for a standard source code-level integrace to command interpretation services. 4. Rationale: it contains information that does not fit well into the great of the decument structure. Posix.1: IEEE 1003.1-1990 adapted by ISO. As ISO/ IEC 9945:1: 1990 standard gives standard for base operating system API. POSix. 16: IEEE 1003.4: 1993 Gives Standard APIS Jos real time OS interface including inter-process common-Pasix:1c: Specifies multi thread programming interface

To ensure program confirms to POSIX. 1 standard user should define \_POSIX\_ SOURCE as 1. # define \_ POSIX\_ SOURCE OR 2. Specify-D\_POSIX\_SOURCE to a C++ compiler. Windows CE: => Windows CE is based on windows 95 with the usual interface, adapted for small devices. The development for this operating system under the code norme peopastis began in 1995. specially designed for micro-computers, the abbrevia--tion CE stands informal for "compact Edition" => The first vorsion of windows CE requires as a minimum 4MB of ROM, 2MB of RAM and a processor of the SuperH3, MIPS 3000 or MIPS 4000 architecture. Windows CE 2.0 came in October 1997 with the fight devices manufacturens étself. TomeType fonts improving now the appearance by the device manufacturers with a display of 640×480 pixel full VGA resolution and 24-bit cdog depts. ET The manageable memory can now be up to AMB. The softward "Handled PC Explore" is renamed to 28 Active Sync.

The update windows CE 2.10 in July 1998 allows the use of TCP/IP and the file system FAT 32with the modular file Wrapper can be incorporated up to 256 different file systems. The RAM can now be up to 16MB.

- The new command line processor allows in this prelease for the first time the use of commands without a graphical user interface. An informed port and USB controller increases the scope.

- •Windows CE30 is only available for ARM CPUS. As new feature the Bhietoott support was introduced.

- windows CEG was interoduced in 2006. It offers a revised kernel architecture of the os. up to 32,000 paralled processes can be executed. A vistual addressable range of 2 Gibyte is possible for every process

The multimedia capabilities have been esopanded and now support HD-DVD, DVD-UDF-25, multichannel audio and much more The compati--bility to existing Windows CE applications and drivens are kept.

Distributed Embedded Systems. • In a distributed embedded system, several Processing Elements CPEs are connected by a network that allows them to communicate. below figure shows an example of a distributed embedded system. Processing elements Processing Element. Processing element (Sensor) Digital signal processing (16 bit CPU) Network Processing elementa Processing elements (ASIC) (ricrocontroller) Distributed Embedded System. · Processing element may includes DSP, CPU 07 microcontroller. Nonporogrammable unit such as the ASICS is also to implement as PE. · By using this entire processing element, it forms bis topology. It is also possible to form other topology also. It is also possible that the system can use more than one network, such as when relatively independent functions require relatively fittle connequication among them. 30

DETET DISTRIBUTED EMBEDDED ARCHITECTURE A distributed embedded system can be organized in many different ways. > The basic element or units \* Processing Elements - DSP, CPU, Sensor Jactuator Asic & micro controller. × Network → The network be any topology, normally bus topology is used. More than one network also can be implemented. → The PEs are connected using communication link. > The system of processing elements and networks forms the hardware platform on which the application sun Sensor 16-bit CPU Actuator PE2 PE1 MICROCONTROLLER DSP ASIC PE3 PE4 PES An example distributed Embedded System -> when analysing network performance - the speed at which PEs can communicate over the bus would be difficult then allowed bus arbitration. -31 -

Scanned with ACE Scanner

The distributed systems are necessary because the devices that the PEs communicate with are physically seperated.

- ⇒ If the deadlines for processing the data are short, then it may be more cost effective.

⇒ An important advantage of a distributed. system is that its several CPUs are in the system, you can use one to generate inputs for another and watch its output.

- i.e good isolation makes easy to diagnose the problem in a part of the system while other parts are working.

Hardware and software Architecture

There are different ways of distributed system depending upon the needs of the application & Cost constraints. They are

- J Point-to-Point communication

- 2) Bus

- 3) General networks.

- 4) Multiple networks.

Point-to-Point communication > A point-to-point Link establishes a connection between exactly two processing elements (PE). > Point-to-point links are simple to design precisely because Itey deal with only two components. -32=> The figure below shows a simple example of a distributed embedded system built from point to point.

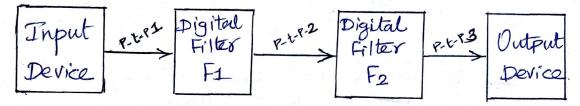

A simple processing system built from Point-to-Point links

→ The input signal is sample by the input device and passed to the digital filler FI, over a point-to-point link (P-t-P link 1).

> The result of the filter is sent through a Second point to point link to the digital filterF2. >The result is then sent to output device over a third point-to-point tink (Ft-P3)

→ Using point-to-point connection allows both F1&F2 to receive a new sample and send a new output at the same time no worny about collisions on the communication network.

## Buses

FIT is possible to build a full-deplex, point-topoint connection that can be used for simultaneous communication in both directions between the two PES-

> In the bus topology, multiple devices to be connected to the like.

> like a microprocessor bus, PEs connected to the bus. have addresses. > communication on the bus uses a form of packets. It contain destination address & diata to be delivered & includes error detection/ correction information as parity. => The header in the packet signals to other PEs that the bus is in use. It is the reeponsibility of the transmitting PE to devide its data into packets; the secering PE must reassemble the complete data message from the packets. Error Correction Header Address Data Format of a typical message on a Bus > Distributed buses must be used the arbitration to control simultaneous access. they are defined as follows \* Fixed-priority arbitration \* Fair arbitration Fixed priority arbitration -> Priority assigned to the devices from High to low + The low-priority device will not able to transmit anything untel the high-periority device has sent all its data packets Fair arbitration -→ Round-Robin asbitration is most commonly used of the fair arbitration schemes. > It requires PCI bus because most implementation of per uses round-robin arbitration.

Scanned with ACE Scanner

General Networks > A Bus has limited bandwidth. Since all devices connect to the bus, communication can interfere with each other. + usually crossbar network is used, because It allows all combinations of input/output connections to be made. >A Crosspoint is a switch that connects an input to an output. > To connect an input to an output, we activate the crosspoint at the intersection between the corresponding input & output lines in the crossbar - Crosspoint A ex ex ex out of PX pX pX pX A CNOSS bor notwork ex ex out 2 et l p \_ out 1 the the the the In1 In2 In3 In4 -> In the above example, to connect In2 80uts crossbar à' should be activated. > The major drawback of crossbar notwork is expensive-> The size of the network grows as the square of number of imputs (if enputs = outputs)

The share the state

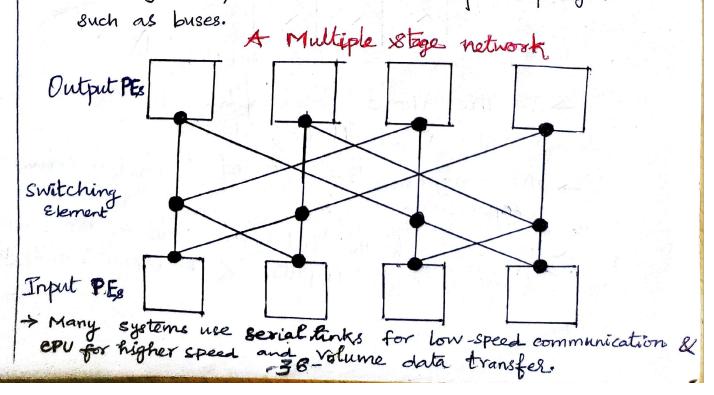

Multiple Networks

-> The crossbar is a direct network in which messages go from source to destination without going through any memory elements. > Multistage networks have immediate Souting nodes to guide the data packets. -> Most networks are blocking, particularly

- A bus is maximally blocking network since any message on the bus blocks message from any other node-

- -> The microprocessor embedded network implement The basic communication functions in partware & sofware.

- > An alternative to a non-bus network is to use multiple networks.

-> The multiple network may be cheaper to use two slow, in expensive networks than single high performance, expensive networks.

> It may be possible to use simpler topologies

## Networks for Embedded Systems

- \* These are several system buses have been used to to build distributed embedded systems.

- \* Multibus and VME were developed by Intel & Motorola, respectively for multicard computer systems and have been widely used in industrial applications.

- \* The ISA bus has been used to support many I/O cards for PC-based ambedded systems.

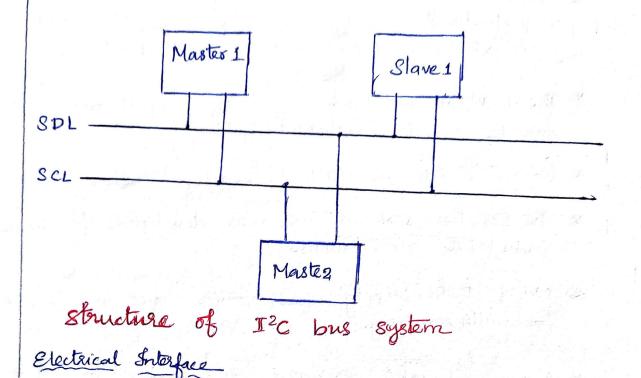

- \* The I<sup>2</sup>C bus is used in microcontroller based systems.

- \* The Echelon LON network was developed for home & industrial automations.

- \* Many DSPs supply their own interconnect structures for multiprocessing.

- \* Many networks designed for embedded networks & general purpose computing.

## The I<sup>2</sup>C [Inter Integerated circuits]

◆It is commonly used to link microcontrollers to Systems.

◆ It has even be used for the command interface in an MPEG-2 video chip; a seperate bus was used for High speed video & setup information is transmitted using I<sup>2</sup>C. Physical Layer

- ♦ Advantages of I<sup>2</sup>C are

- -low cost

- Simple implementation

- moderate speed [ upto 100 kilobits/sec standed bus upto 400 kilobits/sec - extented bus]

- It uses only two lines

\* The below figure shows a typical I<sup>2</sup>C bus system." \* Every node in the network is connected to SDL & SCL. \* One or more than one nodes may be act as master and other nodes are act as share.

- > The bus does not define particular voltages to be used for high or low so that either bipolar or MOS circuits can be connected to the bus.

- A pull-up resistor keeps the default state of the signal high and transistor are used in each bus device to pull-down the signal when Os & 1s to be transmitted.

- > Open collector/open drain signaling allows several devices to simultaneously write the bus without causing destrical demage.

The I<sup>2</sup>C bus is designed as a multi-master bus on various times. As a result, there is no global master.

A master drives both SCL & SDL when it is sending data.

When the bus is edle, both SCL & SDL remain high.

Each master device must listen to the bus while transmitting to be sure that it is not interferring with another message.

Electrical interface to the I2C bus SDL SCL cluck V pata in < Clock DATA INTERFACE CLOCK INTERFACE DATA LINK LAYER : → Every I<sup>2</sup>C device has an address & no two devices in the system have the same address. + A bus transaction is comprised of a series of one-byte transmissions and an address followed by one or more data bytes. - when the master wants to write slave, it transmits the slaves address followed by the data. > An address transmission includes 1. pit- date direction \_ O for writing from the master to slave 7-bit-address Device address RW 1 bit 7 bits + A bus transaction is intrated by a start signal & completed with an end signal as follows: \* A start is signaled by leaving the SCL high & sending a 1 to 0 transition on spe \* A stop is signaled by setting the SCL high & sending a 0 to 1 transition on SPL BYTE FORMAT > The transmission starts when SPL is pulled low while SCI remain high. After this start condition, the clock line is pulled low to intrate data transfer. - 39-

Scanned with ACE Scanner

> At each bit, the clock line goes while the date line assumes its proper value of 0 or 1. > An acknowledgment is sent at the end of every 8-bit transmission, whether it is an address or data > After acknowledgment, the SDL goes o to I while the scl is high, signaling the stop condition. Transmitting a lyte on the I2 bus BUS ARBITRATION : If a device is trying SCL to send a logic 1. but hears a logic 0, it SDL immediately stops txg. & gives the other sender priority. 8-bit Byte start + > If two devices are trying to send identical data to the same address, then of course they never interferes & both succeed in sending their message. Application Interface ATTHE I'c interface on a microcontroller can be implemented with varying percentage of the functionality is hardware & software. Sci ASDL \* The I2c device takes case of generating the clock & data. \* The application code routines (Application) to send an address & a data byte and so on. T<sup>2</sup>C Device which then generates the Microcontroller SCL & SDL, acknowledges, & So forth. Memory \* One of the microcontroller's times is typically used to control the length of in the bus. \* Interrupt may be used to ANI<sup>2</sup>C Interface in a microcontroller recognize bits. \* However, when used in master made, polled I/o may be acceptable if no other pending tasks can be performed. Since master initiates their own transfer.

Scanned with ACE Scanner

| The CAN BUS [Controller Area Network]                                                      |

|--------------------------------------------------------------------------------------------|

|                                                                                            |

| ★ The CAN bus uses bit - serial transmission. ★ CAN can run at rates of 1 Mb/second over a |

| twisted pair connection of 40 meters. An optical unit                                      |

| → The bus protocol supports multiple master on the bus.                                    |

| → CAN provide a good example for a distributed<br>network such as automobiles.             |

| → Each node in the CAN bus has its own electrical                                          |

| drivers and receivers that connect the hoar to                                             |

| the bus is wired-AND fushion.                                                              |

| → In CAN terminology, a logical 1 on the bus is called.                                    |

| recessive & a logical o is dominant.                                                       |

| > The driving circuits on the bus cause the bus to be                                      |

| pulled down to'd' if any node on the bus pulls the bus<br>down (making Odominant over 1).  |

| → when all nodes are transmitting 1s, the bus is said<br>to be in the recessive state.     |

| → when a node transmits a 'O', the bus is in the                                           |

| dominant state.<br>Data are sent on the network in packets known<br>as data frames.        |

| → CAN is a synchronous bus - all transmitters must                                         |

| send at the same time for bus arbitration to work.                                         |

| Hordes synchronous them selfs to the bus by listing to the bit transitions on the bus.     |

| + The first wit of a data frame provides the first                                         |

| synchronization opportunity in a fram.                                                     |

| Data-frame                                                                                 |

| > The data frem starts with a '1' & ends with a                                            |

| string of seven zeroes.                                                                    |

| > The first field in the packet contain's the packets                                      |

| destination address and is known as arbitration field.                                     |

1

.

> The destination identifier is 11 bits long & last one bit is RTR bit (Remote Transmission Request). > If RTR = 0, then read the data from the device specified. by the edentifier. RTR= 1 write operation. > The control field provides an identifer extention & 4-bit length for the data field with a 1, in between > The data field is from o to 64 bytes, depending on the value in the control field. > A cyclic predundancy check (CRC) is sent after the data field for error detection. \$ The acknowledge field is used to inform the reception. is correct or error > when the receiver detects the error, it forces the acknowledgement value to'o' =) If the sender sees a '0' on the bus in Ack slot, it knows that it must retransmit. => The ACK slot is followed by a single bit delimiter followed by the end-of fram field. Physical & Electrical organization of a CAN bus. 1 = recessive 0 = dominant Node Node

The CAN data fram format 1 12 6 0 to 64 16 2 7 Aspitration control Data field CRC field Acknowledge End of tat field field field fram Value 21 Valuezo bit Identifier Data ACK ACK TR length Slot delimiter Code  $\rightarrow$ 11 4 41 Arbitration => The CAN network uses an arbitration using Carrier Sense Multiple Acess with Arbitration on Message Priority [CSMA/AMP]. Similar to the I<sup>2</sup>C bus's arbitration. => This method is = CAN supports a data push programming style. All nodes in the network are simultaneously ' transmit. When a node sees 'O' (dominant bit) in the identifier, it stops transmitting. = By the end of the arbitration field, only ones transmitter will be left. => The edentifier field acts as a priority identifier, with the all 0 edentifier having the highest priority. Error Handling is An error frame can be generated by any. node that detect error on the bus. The current transmission with an error frame which consists of an error flag followed by an error delimiter of

=> The error delimiter field allows the bus to return to the quiescent state. (inactive state) so that from transmission can resume. > The CAN bus provides an over load fram duoing inactive period. is the node sees the overload fram, it stops The transmitting & delayed the for two overhoad frame in a row then it retransmitts. I The CRC field can be used to check a message's data field for correctness. Architecture of CAN controller. Status/control register Protocol Host => Host controller CAN Message. Interface BUS Objects 278 Receive Buffer = The transmitting node retransmits the data from until it gets the acknowledgement An architectures implements the physical & Data link dayer [ since CAN is bus, it does not need network layer] to establish end-to-end connection. the protocol block responsible for determining when to send messages, when a message must be resent due to

arbitration losses, & when a message should be received.

Scheduling algorithm Classification of and other made at a 2010121100 11. Scheduling Algorithm. (1.0) - decisions on what jobs scouts at what Specifico Hans Hartant s about side a Licient to have On-line Schede offline Scheduling dynamie (staticg clockidnined) smith bos 6198ec1 (cropelor) filine and hodule 2) 10 Tengral pussos run teme All postametere ef Static - priority conver - Henan Whans basil Fair, interactive WINK WORKS, SCHED-FIFS) Schediction on ship here at scheduling algo is not Scheduling. (FDF) (JULIS)(mo) twited with emmonly used approaches to scheduling real time s/m's. 1) clock driven cunct Placetiling 2) Weighted round robin sound robin - primarily used for Scheduling seal time traffic in high speed mottched networks Theat set of makes, fixed ministry (Erse met by many Safety- critecal applications 45. Marie 10 autor

Clock driven approach porto 10 mailroipeon) \* decisions are only made at a priority chosen time instantsopth prisbubsilo? (i.e) - decisions on what jobs execute at what times are made at specifice time instants \* It is sufficient to have a h/w timer (no need for OS) \* Regularly spaced time (constants (peniodical) \* Schedule is computed offline and stored for use at run time - All parameters of hard real-time jobs are fixed and known. - Scheduling overhead during runtime is minimal - Complexity of the scheduling algo is not - Good (optimal) off-line schedules can be important found. 1) clock / kinem No flexibility. \* Applicable Only when we know all about the System in advance - Fixed set of tasks, fixed and known task parameters and resource requirements. - met by many Safety-critical applications - Fasier to certify

Weighted Round Lobin Approach Round robin Approach: - (processor - shaving algo) Uses Dured for scheduling time - shared appla. \* when a job ready for execution, it Joins First - In - First - Out (FIFO) Quene \* The job at the head of the queue executes for atmost one time slice, \* If the job dees not complete by the end of the time slice, it is preempted and placed at the end of the queue to wait for its Examples indoit je dilles us proteinites (13 \* when there are "n'jobe, each job gets one time slice every n's time slices, \* Length of time slice & short, the execution of each job starts immediately after it becomes ready \* Each job gets 1/4 the share of the processor when there are 'n' jobs ready for execution \* Hence the round robin algo is called the processor sharing algo.

Mid & Junif R. Might Weighted sound-robin algorithm :-Uses I used for scheduling real time traffic high speed switched Nos - Rather than giving all the ready jobs equal shall of the peocessor, different jobs may given different weights Weights of the job separs to the praction I processor time allocated to the job job with weight wit gets, with time \* a stice every round. \* By adjusting the weights of jobs, we can speed up or retard the peoplers of each job to each \* It is not suitable to schedule precedence Constraint jobs, surce it geves each gob a praction of the processor, sutbali per pipeline jobs to oppose jett gett Norof \* Pilo / A SKA autreas - Milere Here the realist rapic addie to the genericon Maging Mgo

Example :- a in halphalae and edge att the # Consider & Job sets a mansminister lange La production  $\overline{J}_2 = \{\overline{J}_2, \overline{J}_2, \overline{J}$ \* all jobs release time are 0.1 \* their execution times are 1. E sind \* J., and J., execute on processor P. \* J2.2 and J2.2 execute on processor P2. J. 1 is the prederessor of Jiz \* Ja. & the predecessor hold Jar 2 and the bound and the planes J, J.2 \* The WER approved there wet here a scaled printing queue, child a round round ancie P Rit J. 1 & J.g. 1 110 1 distribution & scheduling margage Kansminsseins in JAR & J2.2 Pz 2 0

Priority driven Aredeulaine algorithes \* never leave any resources idle inhentionally \* Scheduling decisions are made when events such as releases and completions of joic rocard inbisso about N.C.S.C. Hence priority driven algo are event driven Otherstames Dworth conserving schedulting. ) greedy Scheduling ; >>>> TO FIRM AN INC. MONALT OF \* Biz IF tries to make tocally optimal decisions \* other a ploces or per resources available and some feb can use it to make progress Such algo never makes the job wait. 2) fist Scheduling \* Implemented by assigning priorités top. \* Jobs ready for execution are placed in one de more queues ordered by the priorities of the fob. \* At any scheduling time, the job coils highest priority are scheduled & executed on available processors

Namp Prival Scheduling algorithes are prionity Non-real Fime 15/m's \* Biheduling decisions and starve asharaking releases and certifications of links FIFO 2 - these algo assign priorities our to populaconding to their chorrest execution elle proviserio irou (ferristrion) Sfirst there algo assign priontic On the Borsis 2 job LETP morsisses recently optimizer decision es resentations avoir la la series Bis can use it to make progress such algo never mater the job coait (9) FROL Schodulinge the Implemented in assimilian

Effective release times and Deadlines \* the gn release times & deadlines of jobs are sometimes inconsistent, with the precedence nove constraints of the job recession of dissilled \* Therefore a sot of effective release times & deadlines are derived from these timing \* The derived timing constraints are consistent with the precedence constraints. Unly one processor priorie sullar musicilism the effective deadlines of rule com and Effective Relaase Time:-Successors . The Effective release time of a job without predecessors is equal to this go release of time de parist autour release of amptions autour be computed in one page fritting precedence graph in O(n.) tune The Effective release time of a job with predecestors, is equally by the maximum Value among itegn release times & the effective release times of all of its precedecessors. ERT pre = Max (RTgn, ERTP)

flechile release times and practimes Effective Deadline other an electronic limer ? The effective deadline of a job without a successor le equal to its given deadline sinter sinter je this is EDws = Dgn , mals and shall not without a successors is equal to the minimum value among its gn deadline and the effective deadlines of all of its the salares string Buccessors . ED = min (Dgn, FDs.) COMMENTS IS COUNT IN THE ON \* The effective release times of all jobs can be computed in one pois through the precedence graph in O(nª) time where 'n' is the no of jobe 117 off \* The effective deadlines can be compared in O(n2) time. (qrad . ppt ) where = my F # (the)

example :- of effective timing constraints into \*  $T_1(210)$   $J_2(1,12)$   $J_4(4,9)$   $J_{5(1,12)}$ 56(0,20) Fig slohestig an algoritam to produ J5(1,82) Joilouris J-7 (62) J2(0,7) Effective RT (raggest) 2 and grande stages J, (2, 10) J3 (2, 12) 11 J4 (419) 2002 J6 (4, 20) Jy (6,21) J2(0,7) J5(2,8) Effective deadline (Smallest) J3(2,8) J4(4,9) J6 (4, 20) J, (2, 8) J2(0,7) > Jy (6,24) 5(2, 8) 55

Disadu \* when there is only one processor and jobs are preemptable, working with ERT & (deadlines allouis us to temposity guore the precedence constraint \* so il possible for an algorithm an invalid schedule to produce (1-0)= \* torberample : J3 5 J, \* This plan is overcome by adding the step to swap the & jobs, the swapping (a) transformer an invalid schedule into a Evalid one (15,0) pt (6,21) is solved at (2, s) = (2, s) , (1, s)

Meril's of Kiority driven

\* Easy to Implement. for \* simple priority algo & these priority algo, the sun-time overhead ( due to maintaining a priority quare of ready jobs Can be made very small. \* does not require the unfo on the release times & execution times of the jobs a priori. This advantage makes it smitable. foi applications with varying time & resource requiements Demerits \* It has not been widely used in hard real time In's (especially safety-orierical 9/m 's). \* Kearon -timing behavior is nondeta ministic when job parameters vory It is difficult to validate that the deadlines of all jobs schedule in a priving driven manner. indeed meet their deadlines

57

Predictability of Executions 1100 0005 \* The Validation phone is easy whenever the exe behavior of the set Tie predictable (ise, no scheduling anomalies) in bo hours HON JUSTION \* Redictability (rompletion times viecording The schedule of I produced by the gn Scheduling algo when the repection time of every job has ilt reaking value the maximal schedoule of 113 of The Schedule of J peopliced by the gr Scheduling afgo when the ere Hume actual minimum malue every job has & the minimal Schedule when the exe time of every job nor actual value, the resultant "Schedule is actual schedule regar Joht od (it)] & actual schedulle the Since the range of exe time of every jos is known, the maximal and mide hall schedules respectively top of J can be besily be considered , tong the \* In contrast, its actual Schedule 1.13/ nunkner blex the actual values of the make aution times are those f(it) = (it) = (it) = t58

\* The execution of 5 Cunder the gribbold priority devien Scheduling algo) is predictable if the actual staget times & actual Somplehon time of every job according to the actual job Hounded by its start times & Completion times according to the making S(Ji) - actual time not Jin pide - St(Ji) and ST(Ji) be the instant fines Tipaccording to the makimal & minimal - Jernis start time predictable set S (Ji) ZS (Ji) ALINS With Hart Schoolder 19 € f(Ji) be the actual Completion time of Ji according to the actual schedule of J ft(Ji) and f (Ji) be the Completion times of Ji according to the maximal & minimal mart, EF article Stational Schedule 1991 Ji la Completion time predictable, if  $f^{-}(J_{i}) \leq f(J_{i}) \leq f^{+}(J_{i})$

\* The execution of Ji is predictable, if Ji is both stant time and completion time predictable.

\* The execution behavior of the entire set J's predictable, if every job in J is predictable.

> era Jy is not completion time predictable, & the s/m is not predictable.

\* execution of independent pre emptable but non-migratable jobs is not predictable.

Validation Algorithms & their performance

- A validation algo allows us to determine whether all jobs in a s/m indeed meet their timing constraints despite Scheduling anomatics.

\* The merits of validation algo are measured in tums of their lomplexity robustness. Accuracy.

• At t=2, Jy has the next highest level (3) 30 it goes next • At t=3, J3, J5, J8 and Jq are released. J5 has the next highest level (2), so it Juns. • At = 4, either Ja or Js could nen b'az both have level 1. But AF this point J2 has already missed its deadline • At ±=5, either J2 or J8 could run • At t=6, J3, J6, Jq are all eligible to run and are all at level o. -+ (Recention -10) Corollary conclusion or swill several Since Jas and Jas missither deadlines This is not a optimal scheduling algo AT BUT FILLE 2) Problem 24 : The Execution times of the jobs in the precedence graph in fig 2 are all equal tol and their release times are identical. Give a nonpre-emptive optimal schedule That minimizes the completion time of all jobs on three placessors! Describe briefly the algo you used to find the Schedule.

61

· At K= 2. Jy has the next Chart Sent geor next R PT han st. Q. The set the R 100 has the next hughed B to blum bit to still halls . I -And have level 1, But H JANC hat chready mutted to dot line E At \$ \$, Elther J, or JS, could rein \* At += 6; Is, Jo, Jg are all phycele to run and and are all at lovel of • Execution time of all jobe equal to 1 Release times are identical Non pre emptire optimal, solutions This is not a optimized schooling algo in public quality and an and south of the so Alpups 112 的感情的 BAC TOPSIAN AS IN 10. 2017 5419 Ane an non pic compting, philipping is superior the participation of the parti Moved skins & The shine buch algo gov used to find the Schedule 62

CHAPTER: 4. Exercises Problem The feasible interval of each job in the  $\bigcirc$ pricedance graph in fig is given next to it hame. The execution time of all jobs are equal to 1. J. (0,10) J. (1,4) J. J. (0,5) andinter ¥ J6(2,10) J4(1,6) GUN . S' 112 1 35.26 Berriel 10 < bien, int have Nit + GML DEGMANNE RIZ KINM J\_8(1,12) -(1)2) Jy(1,12) int willing the Sillie (a) Find the effective release times and deadlines of the jobs in the precedence graph. Sohn :- ERF. & ERGY, 100 (5 SINIT SXF. J, (0, 4) - J2(1,4) J3 (3,5) de 10 J\_(3,3). J. (3,18) J4(1,4) NOTIONOLON beenslos attilized, Ja (3,12), Ja any jobs released at t=0. Je has a level of 3, so it goes 63 12

## CHAPTER: 4. Exercises Roblings

John Som: - execution fime of all fob = 12 brief

0 1 2 3 4 5 6 7 8 9 10

I A job is Said to be at level i, if the length of the longest path from the job to jobs that have no successors is i sappose J3, J and Jg are at level o, jobe J2, J5 and J8ar at level 1, and so out. Suppose that the priorties (CIL) For the jobe are assigned based on their levels the higher the level, the higher the priorih Ind the priority driven Schedulen of the jobs in Fig 1. according to the perprint assignment. the time of all jobs is 1. (t, e) U -(4)(0)74 MADLE Jo J4 J7 J5 J2 J8 3 36 5 6 (1) ] ]. 8 9 10 J. Y 3,18) Explanation (4,1) T (c)  $f_{i}$   $f_{i}$  Ty has a level of 3, so it goes first 64

Jobs medit scheduleds on they Lonsur Pz septain meet there charly no 2010 2 01 Problem 3 :- A s/m containe 9 nonpreemptable execution times are 12. Ji is the immediate predecessor of Ig, and If is the immediate Predecessor of J5, J6, J7 and J8. There is no other precedence constraints. For all the jobs Ji has a higher priority than JK if izk. dear the isprecedence graph of the SUL pobs gehedule them prequiptable & +Rew. Spelatin un ansit Spel5 J2 J4 pb 65

b) Can the jobs meet their deadlines if they dore scheduled on the processor? Explain your answer. Som: - All jobs meet their deadhine 4 5 6 7 2 mits/11 1 1 1 10 (1 hablen 3 sand MANUP SEANT J3 JI is the execution struct - new KND5P FA HOUTALD The Jun Ja p Reade case on at I.T. In and Je Allere J8 CALLER STORMET c) Can the jobs meet their deadlines if we make them preemptable & Schedule them preemptively? Explain us ansi she Jobs Ja does not meet its deadline dead Jg P JA TTR Jb lg B J9 1 4. JI Ja P3 J2 Jy 66

d) Can the jobs meet their deadline, 16 they are scheduled non-pre-emptively on 1 plocessors? Explain us answer. solu Tob Jg does not meet its deadline 23456789 12 13 14 15 11 10 16 Jg JI JE Jg 19 J2 > deadling 50 JS P2 CP Strate J4 At a Real Library 2) Suppose that due to an improvement of the three processors, the execution time of every job is reduced by 1. Can the jobs meet their deadlines? Explain your answer? for Job Jg does not meet its deadline 0 1 2 3 4 5 6 7 8 9 10 11 12 13 Ja 25 J P Jo

Scanned with ACE Scanner

110 Intensive S/m Derigin:-\* 10 devices. \* processing the data locally by shipping the data over the n/w. \* Inventory the required 10 devices \* 1/0 devices that do not require local processing may be attached to the N/w with simplest available Intrilace available Intuface \* Determine which devices can shake a PE de nho interface stores \* Analyse communication times to determine whether catical comm may interfare with each other. \* Allocate minimum Pt with each 15 devices A Design rest using computation intensive s/m's procedure. Compartiation Jutensive S/m design?-\* Consider the process and their deadlines and communication \* taske with Shortert deadline Require own PE element. \* Analyse communication times \* Allocate Lower-priority toute to shared PEs where possible.

Yower consumption of other requirements reallocating processes!! boad balancing. our alsta AND INSTRUMENT Elevator controller land hall and -) distributed system design era The components are physically distributed among the elevators and floors of the building & the s/m "must meet, both, hard a soft deadlines sind sequesting keeponding to Making sure the elevator monthly mis priced requestor for the right pt) · Julining elevator) Theory - Mr omnipunketeeri luhensirie : Marst Tissilli. L'Elevator carl istraige y \* Carries possenger the house any quins up & down the house ay N - no. of hoistway + Auchyse communication F' - no q Floors Allocale Lecurat price il to have power to 69

Summing up the worst case execution times of the processes to=  $\sum_{provensi i T_i} \frac{T_i}{T_i} + p_i /_2$ tp? ) execution time of process P?. ne ⇒ Lom of all periods Transfield producel \* we can compute the communication volume Over the LCM of all periods . Ne = Z Le Process int bir Party 4 - This formula Computes the total no. of bytes transmitted is son somercing rop shitsing Two strategies ( efficient c/m jou our design) \* 2/0 intensive s/ms: somerceptor instal - start with the 1/6 devices & their associated processing in him in \* Computation - intensive 3/mso: 7 Asupitation have start the process point how meeds of this she can be etterined

Hardware platform Derign, Allocation & Scheduling hardware Schedule allocation of peocess Hardware platform shiring lip joinst of smiles # No. of PES required ins) hus su \* types of all PESIS por mole sult parts \* No. of notworks required \* types (and data rates) of the n/cos. \* To evaluate the platform, allocation 21 Schedule for processes are need to be Conskuted \* allocation & scheduling are driven by System prejormance Analysis malar de r Stealty His So devises 21 their - computation & communication need of the s/m Computational needs submit intustingues of \* A lower bound on the computational needs of the s/m can be obtained by

MPSoc's and shared Memory Multiprocessors \* Multipuccessor is parallel processors with a single shared memory. \* Mpsoc are used to build complex integrated system. \* Multiprocessors have me highest absolute performance-faster than the fastest uniprocessor. \* parallel processing system is a sigle program that runs on multiple processors simultaneously. \* claster is a set of computors connected over a LAN that functions as a single large multiprocessor. \* Typical Mpsoc is a heterogenous multiprocessor. \* Menory conholler : interbaces with the Embeded. Software API onbound RAM memory \* DMA Handles automated transfer of data. MPU/CPU 3 USB controlly: manges the hardware side. configurable 4. DSP core: provide hardware acceleration handwale DSP Interback core 5. Display: Enables the soc to drale peripheral ASIC various display types. ADE 6. Camera: Allows the soc to interbace with DAC a camera. 7. Storage: manages I/O with the various RF/IF subsystem types of storage. Fig: System on chip 8. Debug: Enables the soc to be connected to hardware debugging tools through various mechanisms, such as JTACZ. CPU 1 (CPUZ) ···· (CPUN Fig: Shared Inter connection Network Memory main main memory 2 main Main N memory 3 ... memory N memory \*Signal address: offer the programmer a single memory address space that all processors share. \* sig Message passing: Communicating between multiple processors by emplicitly sending and receiving message. only one or \* Heterogenous memory system some memory blocks are excessible by few processors + Jaregulas memory structure are often necessary in MPSOCS. Challenges and opportunities. \* MPSOCS combine the dufficult of building complex hardware & software systems \* Methodology is califical to MP50c design. + configurable processors with customized instruction set ablone way to -Improve 1 characteristics. 81

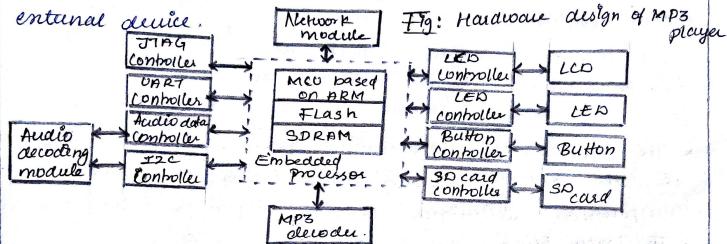

Design Example : (1) Auctio Player

\* Audio players are often called MP3 players after the popular audio data format. An MP3 player performs three banc functions: audio storage, audio decompression, and user interpace.

\* The MP3-player is mainly made up of focus parts, which are embedded processes, interbace module, storage and

\* The most important hardware module in MP3 player is the decoder module.

\* with the scapid development of processor design and related fechnology, the capability of digital signal processing of RISC approaches WSP level in the last few years.

\* Therefore, it is of vital importance to implement MP3 decoder based RISC core. On the other hand, a RISC core can be used to as both audio decoding unit and control unit, it is useful for resource constrained system on chip design.

\* Our MP3 devoder reads the MP3 file and sends the samples through 725 intubace.

## Dideo Aculerator

| where                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | <b>12</b> 1 83 5.                                                                                                                                                        |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | * It has 16 PEs that perform the difference<br>calculation on a pair of pinels.                                                                                          |

| Statement and a statement of the                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | * The machine consists of two memory: macrobiock<br>memory and secuch memory.                                                                                            |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | * The machine country                                                                                                                                                    |

| no become address a co                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | Comparator                                                                                                                                                               |

| and the real (second second                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | PEIS                                                                                                                                                                     |

| Na Star Maruna Amerikan                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                                                                          |

| Considering some special                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | Network Conbol Network                                                                                                                                                   |

| The second second second second second                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                                                          |

| Contraction of Street of Street                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                                                          |

| and the second second second                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | closely as possible. Address generator Fig: Architecture for the<br>motion estimation accelerator                                                                        |

| and a second advance of the                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | or more reference frame to match the current frame as                                                                                                                    |

| distribution of the local data                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | a motion vector is computed.<br>The motion estimation creates a model by modifying one                                                                                   |

| and the second se | * For each block of 16×16 l'uninance pels, in the current brand,                                                                                                         |

| and the second se | compression technique is used, known as much fume wing                                                                                                                   |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | is also known as inter-prame coding. A isecond                                                                                                                           |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | * The nuccess of video compussion using motion estimation                                                                                                                |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | can be described in terris of                                                                                                                                            |

| A COMPANY OF A COMPANY OF A COMPANY                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | * Block motion estimation is that one frame in the video<br>compression algorithms so that one frame in the video<br>can be described in terms of the difference between |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | is used in degial ndeo                                                                                                                                                   |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | time to find the work the                                                                                                                                                |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                                                          |